# FASTIME: A Multi-Channel 130 nm CMOS ASIC for a Complete Fast and High-Resolution Time Measurement Chain

Mokrane Dahoumane (m.dahoumane@ip2i.in2p3.fr), L. Alvado, N. Arveuf, R. Bonnefoy, L. Caponetto, T. Chaventré, X. Chen, S. Drouet, F. Druillole, F. Jouve, I. Laktineh, L. Leterrier, S. Manen, H. Mathez, M-L. Mercier, A. Mhoudini, M. Morenas, G. Noel, L. Raux, P. Russo, C. Sylvia, P. Vallerand, R. Vandaele

**Motivations**

FASTIME is a multi-channel ASIC providing a complete time measurement chain with a precision target of the order of 1 picosecond for 1 pC input charge and a dead time less than ten nanoseconds. Such resolution becomes necessary in various fields such as future particle physics experiments at FCChh to mitigate the expected pile-up of 1000, or in future generations of medical imaging (PET) to reduce significantly the dose injected into patients. It will also be needed to exploit a new type of sensors with high temporal resolution called NanoChannel Plate (NCP).

## **Circuit description**

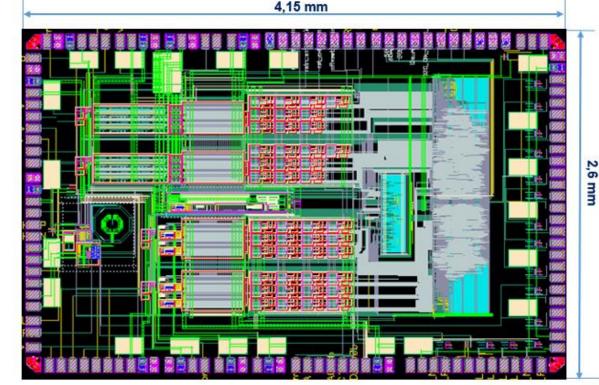

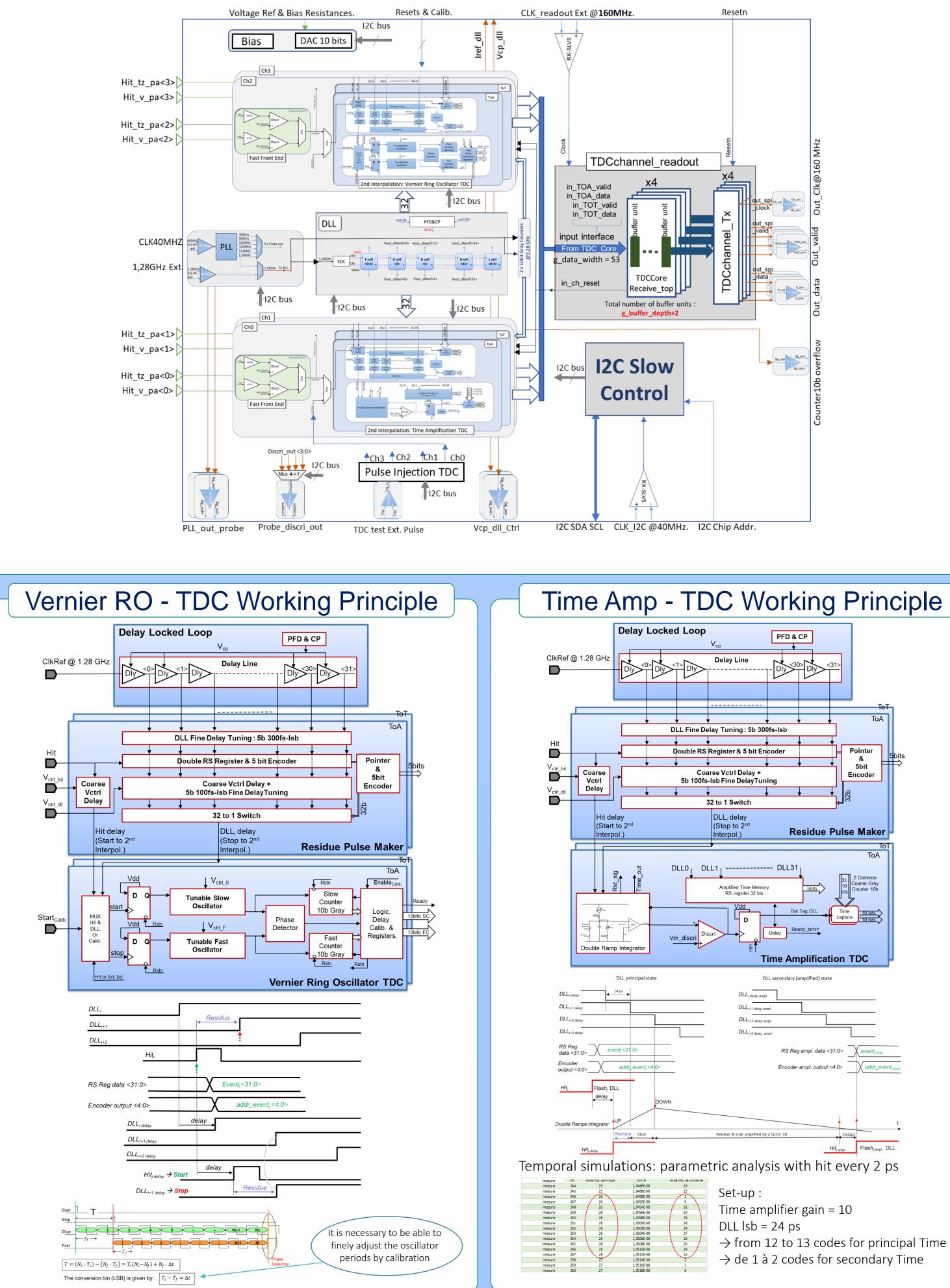

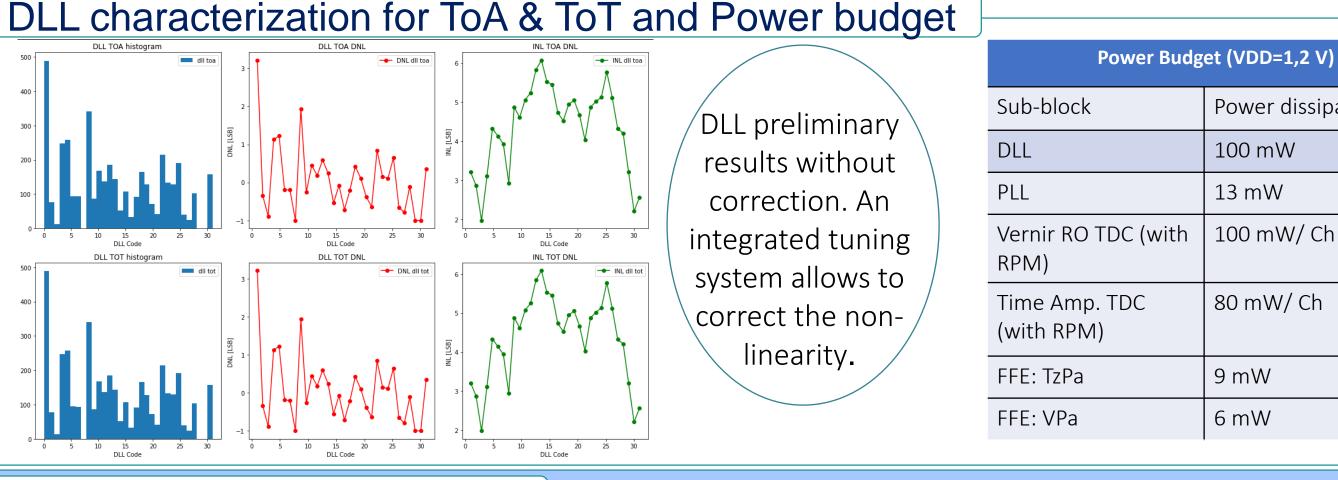

This prototype was produced in the 130 nm CMOS process. It consists of 4 channels; each one comprises a Fast Front End (FFE) stage coupled with a discriminator followed by a Timeto-Digital Converter (TDC) with double-level time interpolation. A 10-bit coarse counter provides 800 ns on-chip dynamic range. The first interpolation level of TDC is based on a Delay Locked Loop (DLL) with 32 differential delay elements operating at 1.28 GHz reference clock, which is generated by a sub-ps jitter on chip PLL, allowing a quantization step of 24.4 ps resulting in a theoretical accuracy of 7 ps rms. To refine the DLL temporal precision, a second level of time interpolation is added using two different TDC architectures, Vernier Ring-Oscillator TDC and a Time Amplifier TDC, both with an LSB of 3 ps. An intermediate circuit called Residue Pulse Maker generates the start and stop signals needed for the 2nd level interpolator. The FFE stage also integrates two preamplifier architectures: a Voltage Preamplifier and a Trans-Impedance one. The ASIC is fully configurable via slow Control (I2C). A digital readout block performs initial data processing and serializes TDC data in differential mode with an output clock of 160 MHz. Each channel measures both ToA and ToT, the latter is used to compensate for time walk.

## Test Results

The circuit was manufactured in early 2023 It occupies a 2.6x4.15 mm<sup>2</sup> area including PADs. Testing has progressed well. The qualification of this ASIC requires meticulous work in calibrating the oscillators of the Vernier TDC, the DNL of the DLL, and the parameters of the Residue Pulse Maker (timing of start & stop signals), as well as the gain factor of the time amplifier.

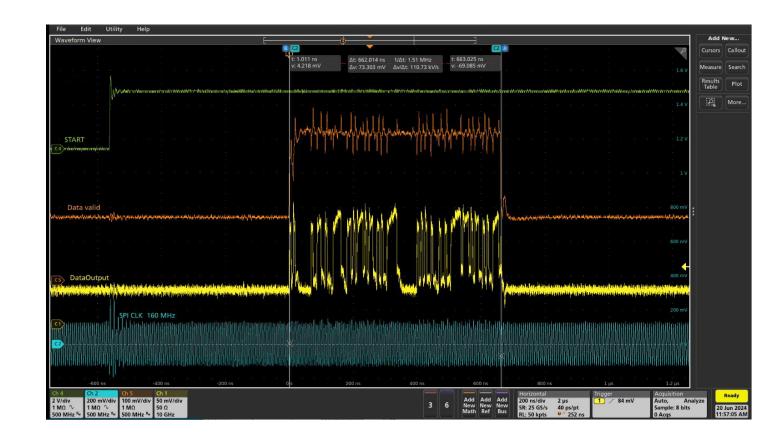

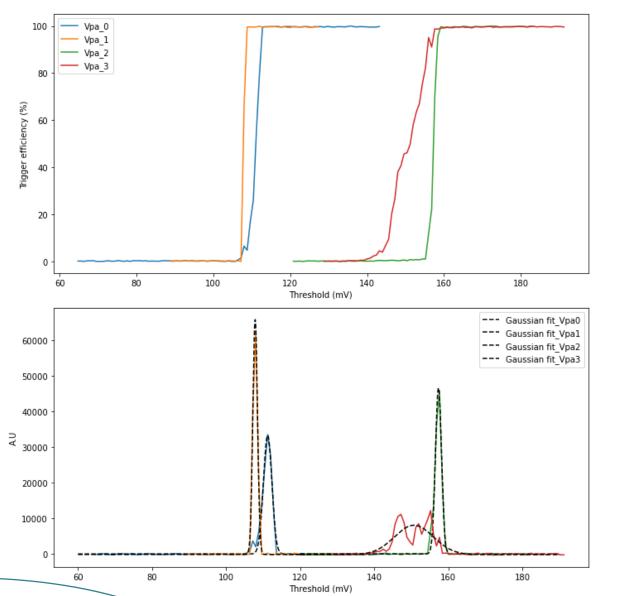

**TDC output data frame:** on a start signal, the TDC sends a 106-bit serial data signal including ToA and ToT, a DataValid signal as well as the serialization clock at 160 MHz. This plot demonstrates the good working of the whole chain.

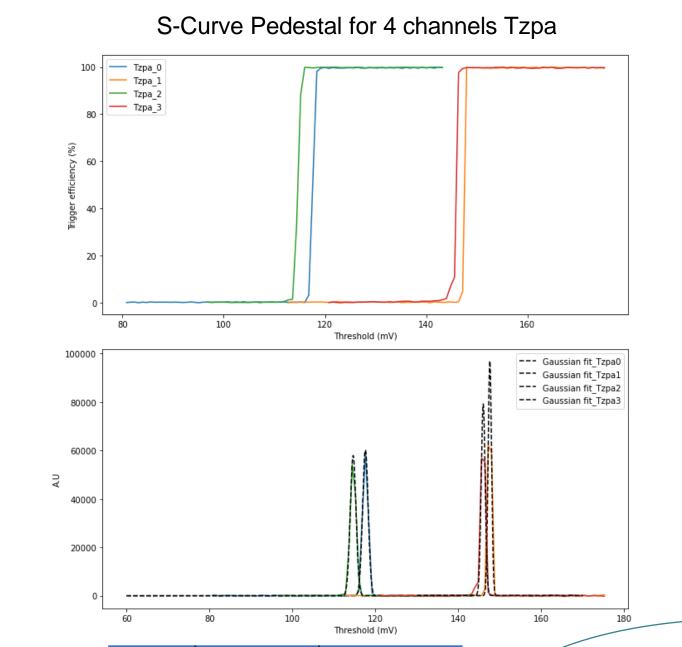

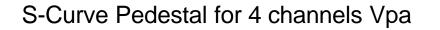

## **FFE&Discriminator test results**

PLL @ 1,28 GHz: The integrated PLL achieves 1.7 ps rms Jitter in test. This amount cumulates the Clock reference input jitter. The simulated jitter is less than 1 ps rms.

Mean (mV) StdDev (mV)

0,81

0,441

0,58

3,70

Power dissipation

100 mW

13 mW

100 mW/ Ch

80 mW/ Ch

9 mW

6 mW

111,2

107,8

157,3

150,7

# $\rightarrow$ from 12 to 13 codes for principal Time

## Test Bench

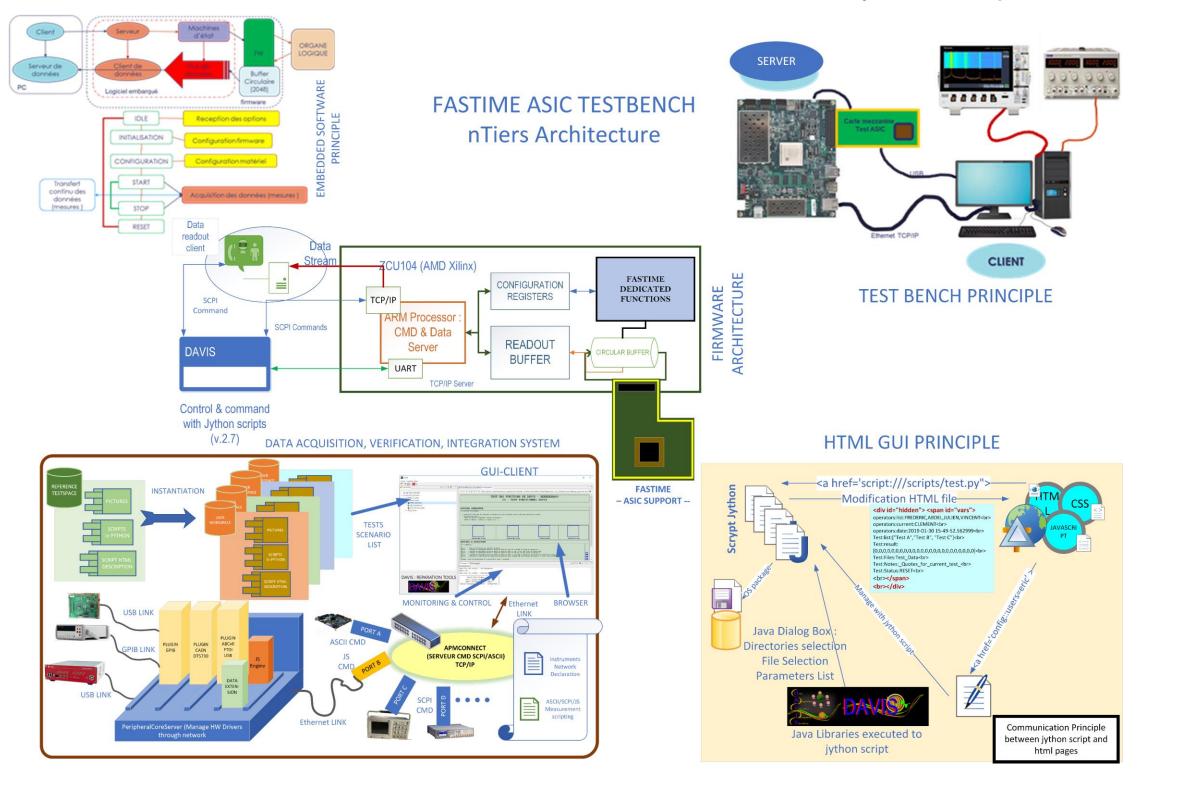

The TB setup is based on an FMC mezzanine card paired with an AMD ZCU104 FPGA card for I2C control of the ASIC and SPI data acquisition. Embedded software running on the ARM microprocessor, developed in C, enables a TCP/IP server for Unicode commands. These commands allow for the configuration of ASIC registers and control of instruments associated with the tests. On the PC side, a client, following an n-tier architecture, enables the user to write test scenarios in Jython scripts

| Тzра | Mean (mV) | StdDev (mV) | The Transimpedance Pream          |

|------|-----------|-------------|-----------------------------------|

| 0    | 117,5     | 0,479       | The Transimpedance Preamp         |

| 1    | 147,58    | 0,292       | performs a slightly better result |

| 2    | 114,63    | 0,488       | than Voltage Preamp.              |

| 3    | 145,9     | 0,340       |                                   |

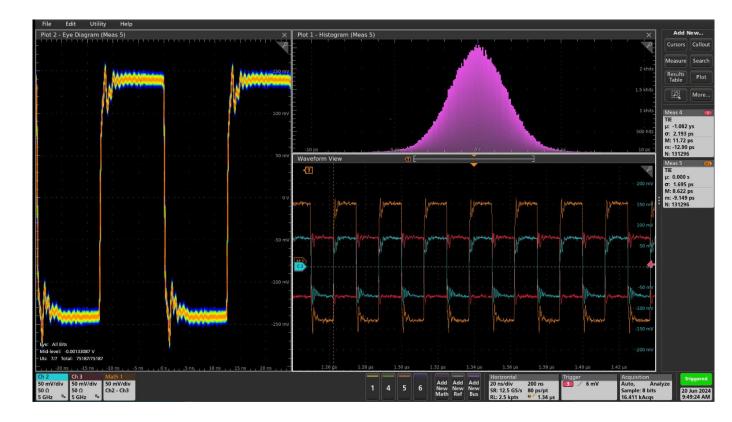

Jitter Channel 1: 11 ps rms Jitter for ToA of Voltage Preamp with 0,75 pC input Charge. The simulated jitter is less than 1 ps rms for 1 pC input.

| Channel<br>number | Tzpa Jiter<br>(ps rms) | Vpa Jiter<br>(ps rms) |

|-------------------|------------------------|-----------------------|

| 0                 | 24                     | 13                    |

| 1                 | 20.7                   | 11                    |

| 2                 | 21                     | 13.5                  |

| 3                 | 19.5                   | 12                    |

Vpa

1

**Jitter of all channels**: jitter of the Tzpa is less the injected charge is not entirely good, transmitted to the preamp. a part is lost in the parasitic capacities of the asic case

## Conclusions and perspectives

The circuit is currently being tested. Preliminary test results are promising and validate all circuit functionalities and features. More detailed and exhaustive tests such as the noise, jitter, crosstalk, linearity, readout speed, testing set up and methods are in progress.

Dedicated software is being developed to automate tests and carry out statistical studies. A human machine interface was designed using DAVIS (Data Acquisition, Verification, Integration System) software to facilitate interaction with the different design blocks.

The FFE jitter is higher than simulated values, we are exploring the possible causes and sources of this degradation. A new version of analog mezzanine test bord has been designed, the asic will be directly wire bonded without any packaging in order to reduce input capacitors, wire bonding self etc.

In this design, all blocks can be tested separately. TDCs can be tested directly with an external trigger signal, in order to isolate the performance of the TDC from the impact of the FFE jitter.

## References

[1] ECFA WP4.2 of DRD4 collaboration https://petvision.ijs.si/ecfa-drd4-constitution/

[2] Paul Lecoq et al 2020 Phys. Med. Biol. 65 21RM01

[3] L. S. de Paula, et al. "A wide band CMOS differential voltage-controlled ring oscillator," 2008 Joint 6th International IEEE Northeast Workshop on Circuits and Systems and TAISA Conference, Montreal, QC, Canada.