ATHENA X-IFU WFEE

D. Prêle CoI X-IFU, Si Chen Responsable Design IC, Jean Mesquida Designer, Manuel Gonzalez Instrument Scientist, Bernard Courty EGSE – APC

La mission Athena (Advanced Telescope for High ENergy Astrophysics) est la deuxième mission spatiale de type Large (L2) du programme à long terme Cosmic Vision de l’Agence Spatiale Européenne (ESA). Cette mission s’inscrit dans le thème scientifique The hot and violent Universe. Actuellement en phase B (phase de definition préliminaire), une « adoption » de la mission mi-2027 engagera la phase industrielle du projet suivie d’une phase de construction qui aboutira à un lancement autour de 2037.

L’électronique de proximité « chaude » Warm Front End Electronics – WFEE de l’instrument X-IFU d’ATHENA est depuis le début de la Phase A (2015) sous la responsabilité de l’APC. Le coeur du WFEE est construit autour d’une famille d’ASIC “AwaXe” permettant :

- la polarisation bas bruit des détecteurs supraconducteur TES

- l’amplificateurs à très faible dérive de gain des signaux en sortie de cryostat

- l’ajustement des points de fonctionnement des étages de lecture cryogéniques (SQUID)

R&T BiCMOS

D. Charrier Subatech – porteur, D. Prêle APC – co, L. Alvado LPC Caen, E. Bechetoille IP2I, S. Chen APC, L. Leterrier LPC Caen, J. Mesquida APC, P. Russo IP2I, B. Ton, M. Gonzalez APC

Un nombre de voies de lectures croissant et la nécessité d’intégrer toujours plus de digital dans les ASICs front-end conduisent au choix de technologies purement CMOS sur des nœuds de plus en plus fin en 65 ou 28nm. Néanmoins, il reste des domaines où il est difficile voir impossible de se priver de transistor bipolaire ou à minima de noeuds CMOS pas trop fins que ce soit pour des raisons de bruit à basse fréquences, de dynamique ou de produit gain-bande. Par ailleurs nombres de détecteurs que ce soit en physique nucléaire, en astrophysique ou pour des applications médicales n’exigent pas des densités d’intégration aussi fortes que la physique des hautes énergies du LHC.Un premier travail de recensement des types de détecteurs susceptibles de bénéficier d’une technologie BiCMOS a été fait. Ce devrait être le cas par exemple de détecteurs fortement capacitifs en physique nucléaire ou faiblement résistifs en astrophysique principalement pour des raisons de bruit.

Un objectif de la R&T BiCMOS est donc la recherche et l’évaluation d’une ou deux technologies BICMOS/CMOS de référence qui réponde à ces contraintes techniques. La technologie sélectionnée doit aussi être pérenne et à coût contenu pour être accessible à l’échelle d’un laboratoire ou d’une petite équipe.

Un second objectif de la “R&T” est une comparaison des performances d’un large panel de technologies CMOS/BiCMOS par la simulation de facteurs de mérites tels que l’efficacité de transconductance, l’efficacité de vitesse, le gain intrinsèque, le produit gain bande, le ratio dynamique sur bruit. En répondant à ces deux objectifs, la “R&T BiCMOS” s’inscrit pleinement dans le workpackage WP1.1 “technologies alternatives” de la Mi2i.

Le dernier objectif est de créer une synergie autour du nœud sélectionné afin de rationaliser les ressources humaines et logiciels sur les développements d’ASIC et par la mise en commun de fonctions de bases et de Design Kit en s’appuyant sur les infrastructures de la Mi2i et celles du projet OMMIC.

Une première fonderie avec des fonctions de base tel que des LNA, TIA, amplificateurs CMOS, thermomètre et transistors élémentaires a été lancée sur le noeuds IHP 130nm SG13S à des fins d’auto-formation et pour vérifier si les résultats de mesures sont fidèles aux simulations. Les technologies XFAB en 180nm sont aussi candidates et font l’objet d’un travail d’évaluation. Ces résultats ainsi que le travail comparatif par les facteurs de mérites sera documenté et publié.

R&T LoJiC130

Top-down design methodology for a 2 ps rms Jitter at 2.56 GHz of an analog PLL based on Ring and LC Tank Oscillators

E. Bechetoille𝑏 ; B. Joly𝑐 ; O. Lemaire𝑎 ; I. Laktineh𝑏 ; S. Manen𝑐 ; H. Mathez𝑏 ; P. Russo𝑏 ; P. Vallerand𝑎 et R. Vandaele𝑐

𝑎 : ILClab, Université Paris-Saclay, CNRS/IN2P3, IJCLab, 91405 Orsay, France

𝑏 : IP2I, Université Lyon, Université Claude Bernard Lyon 1, CNRS, IP2I Lyon/IN2P3, UMR5822,F-69622, Villeurbanne, France

𝑐 : LPC Clermont, Université Clermont Auvergne, CNRS/IN2P3, LPC, F-63000 Clermont-Ferrand, France

A top-down methodology is proposed to design Phase-Locked-Loops (PLL) using behavioural and transistor-level simulation in two cases: Ring-Oscillator (RO) and LC Tank Oscillator (LCTO) with the aim to achieve a low-jitter PLL clock generator in 130 nm process. The optimization of these two PLLs is obtained in three steps. The first one is to design a model in Verilog-A of each block with its intrinsic jitter parameter. Each block is simulated alone to verify the nature of its intrinsic jitter: Frequency Modulation jitter (FM jitter) or Phase Modulation jitter (PM jitter). The second step is to place each of these blocks in a global schematic to obtain a full behavioural PLL. In this way, one can study the PLL operation and check the effect of each block’s jitter on the PLL output. The third step is to use the intrinsic FM jitter or PM jitter values to simulate at the transistor level of each block individually and then all of them together. To evaluate the loop bandwidth and the loop stability of each of the two PLLs, a linearized PLL is designed using ideal sources. This approach is important to check the compatibility of each block in terms of jitter and bandwidth with respect to the target PLL performance. The optimization results are used to design and produce two PLLs. Measurements of these two are found to have an absolute time jitter of the order of 2 ps rms

Contact : h.mathez@ipnl.in2p3.fr

R&T Fastime

L. Alvadod ; N. Arveuf𝑐 ; R. Bonnefoy𝑐 ; R. Bouetf ; L. Caponetto𝑏 ; X. Chen𝑏 ; A. Contamine𝑐 ; M. Dahoumane𝑏 ; S. Drouetd ; F. Druillolef ; C. Fayard𝑐 ; I. Laktineh𝑏 ; F. Jouve𝑐 ; L. Leterrierd ; S. Manen𝑐 ; H. Mathez𝑏 ; M. Mercier𝑐 , M. Morenase , A Mhoudini𝑎 , L. Rauxe ; P. Russo𝑏 ; C. Sylvia𝑎 ; P. Vallerand𝑎 et R. Vandaele𝑐

𝑎 : ILClab, Université Paris-Saclay, CNRS/IN2P3, IJCLab, 91405 Orsay, France

𝑏 : IP2I, Université Lyon, Université Claude Bernard Lyon 1, CNRS, IP2I Lyon/IN2P3, UMR5822,F-69622, Villeurbanne, France

𝑐 : LPC Clermont, Université Clermont Auvergne, CNRS/IN2P3, LPC, F-63000 Clermont-Ferrand, France d : LPC Caen, Université de Caen Normandie, ENSICAEN, CNRS/IN2P3, LPC Caen UMR6534, F-14000 Caen, France e : OMEGA, CNRS, École polytechnique, Institut Polytechnique de Paris, 91120 Palaiseau, France f : LP2I Bordeaux, CNRS/IN2P3, 33170 Bordeaux, France

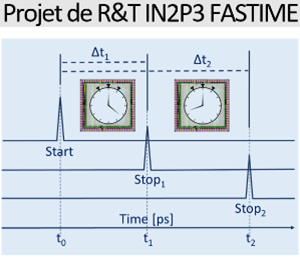

FASTIME est un projet de R&T/IN2P3 démarré ne 2021 qui porte sur le développement d’une électronique intégrée (ASIC) de mesure de temps très rapide de résolution de l’ordre de la picoseconde. Une telle résolution devient de plus en plus nécessaire dans de nombreux domaines : par exemple, dans les futures expériences de physique des particules pour réduire le pile-up de ~1000, ou dans les futures générations d’imagerie médicale (TEP) pour réduire de ~20 la dose injectée dans les patients ou enfin pour d’autres applications sociétales (détecteurs pixels précis dans le temps) dont la résolution temporelle inférieure à 1 ps rms ne doit pas être dégradée par l’électronique de lecture. Cette proposition s’appuie sur l’expertise et sur la synergie de plusieurs laboratoires de l’IN2P3 et offre ainsi un cadre collaboratif pour proposer des solutions novatrices et murir une technologie porteuse au-delà de l’existant.

L’objectif de ce projet est de réaliser un prototype d’ASIC multivoies qui intègre une chaine complète de la mesure de temps en deux phases principales. Pour la réalisation physique du circuit, nous avons sélectionné la technologie TSMC 130nm pour sa maturité et sa pérennité, ses performances, sa grande tenue aux radiations validée par le CERN. Ce choix technologique a également été motivé par l’expertise de la communauté IN2P3 dans cette technologie nous permettant de s’appuyer sur des bases solides. Le transfert de ce design vers des technologies plus fines, comme la TSMC 65nm ou la FD-SOI 28 nm, restera réalisable.

L’étage de Front end comporte deux architectures de préamplificateurs rapides (un préampli à transimpédance et un préampli en tension)et un discriminateur avec 1 ps rms de résolution pour une charge de 1 pC. L’étage TDC est composé de deux niveaux d’interpolation offrant une précision totale de 1 ps rms. Une DLL avec un pas de quantification de 24 ps constitue le 1er étage d’interpolation. Le résidu de cette mesure est extrait par un bloc spécifique et est envoyé sur un 2ème étage d’interpolation réalisé avec deux architectures différentes : un TDC à Vernier Ring Oscillateur et un TDC à Amplificateur de Temps, avec 3 ps de LSB chacun. Tous les paramètres du chip sont configurables par I2C. les data de al mesure sont sérialisées et sortie en différentiel grâce à un circuit SLVS.

Cette R&T permettra donc de faire une étude comparative entre les différentes options. Les résultats de test de la phase 1 du projet sont très encourageants et ont fait l’objet de présentation Poster à la conférence IEEE NSSMIC-RTSD 2024. Une version 2 de FASTIME (phase 2) moyennant des modifications mineures est prévues fin 2025. La documentation technique est systématiquement rédigée à chaque étape de travail dans le projet. Les résultats et les études seront publiés dans un journal.

Contact : m.dahoumane@ip2i.in2p3.fr